|

IC芯核随工艺尺寸的不断缩小正迅速缩减,唯一的例外就是芯片的I/O,0.5umCMOS工艺技术以后I/O尺寸基本上维持不变。当前新的紧密型静电释放(ESD)设计技术能缩减I/O尺寸,进一步减小IC芯核的大小。

在半导体的生产中,主要的成本来自于晶圆面积的占用。如果能在一个晶圆上实现更多的器件将显著降低成本,这也是促进IC芯片特征尺寸不断缩小的主要动力。过去的十年时间里,IC芯核尺寸很大程度上得到了减小,在更小的硅片面积上可以实现更多的功能。但是,在IC设计中I/O面积并没有显著的变化。

由于输入-输出晶体管实现IC芯核内部的小信号(微安级)与周围电路子系统(信号大小为毫安级)之间的通讯,通常这些晶体管的尺寸都非常大,同芯核中1微米大小的晶体管相比较,这些I/O晶体管尺寸可能大到几百微米,因此为了减小芯核面积,设计工程师必须解决I/O晶体管的尺寸问题。

另外,静电放电电流通常达到几安培,为了保证IC的性能,在芯片设计中必须引入强制性ESD保护措施,这在一定程度上加大了I/O的设计尺寸。

为大电流静电放电提供合适的镇流(ballast)通路才能实现ESD的设计保护。传统的做法是用敏感器件(绝大多数情况下是NMOS晶体管)里的活性硅间隔来实现镇流电阻,这种解决方法增加了很高的成本:镇流电阻占用较大的硅片面积,而硅片面积的增加增大了IC设计的成本。

当前,新的ESD设计技术解决了这个问题:镇流电阻可以通过高效的面积使用方法来实现。新的设计方法能确保实现较小的I/O,更小的IC芯片尺寸,因而每一个晶圆上可以有更多的IC,从而降低产品的生产成本。

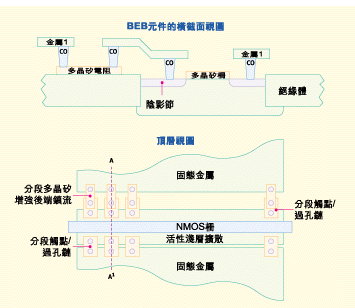

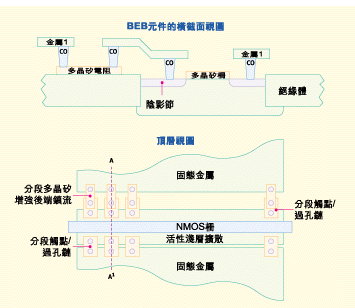

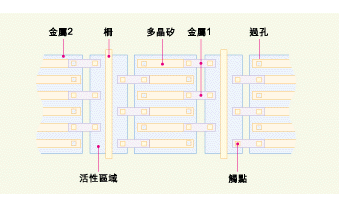

新的设计方法采用分割器件设计的后端镇流(BEB)、整合的镇流电路(MBC)版图设计以及多触点电路设计(MFT)组成。与传统的工艺技术相比较,典型的0.18微米工艺技术中BEB、MBC以及MFT的结合可以实现以下的效果:ESD性能提升超过60%;电压箝位效率提升超过30%;接通电阻改善50%;面积使用效率改善2到3倍。

这种硅片设计解决方案可以实现100%的CMOS兼容,而工艺不需任何改变,也不需要制作任何特殊或者额外的掩模。事实上,改变三个20年来传统的思维模式可以很容易理解这种设计解决方案。

第一,实现片上ESD鲁棒性并不需要活性区域镇流(activeareaballast)或者硅化物模块。

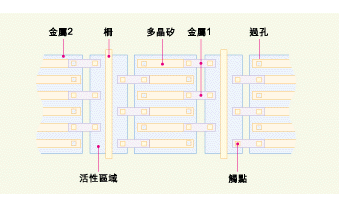

为增强ESD鲁棒性的镇流并不需要较大的硅化物模块或者活性区域来实现。可以使用工艺技术中后端的要素,比如与硅片之间的触点,与多晶硅之间的触点,以及硅化的多晶硅来形成镇流网络。这种实现方法的关键是引入了镇流电阻的“分割”:使用多个并行的大电阻来形成一个全局的具有低串联阻抗的ESD鲁棒性器件,如图1和图2所示。这种技术不仅提供很高的ESD性能,而且也不需要硅化物模块。

模拟电路设计工程师经常使用硅化物模块来实现精密电阻。这样的好处在于极大地降低了漏区到阱区之间的寄生电容:比较一个最小尺寸的漏区扩散和一个3微米到4微米有源镇流的漏区扩散,这种方式可以工作于任何宽度尺寸的I/O晶体管。

第二,镇流区域可以共享,较大的驱动器可以用相对较小的硅面积来实现。

当不用活性区镇流就会存在介质隔离电阻。硅片实现已经证明并不一定需要某一个最小尺寸空间电阻来提供必需的ESD性能。将这一最小尺寸增加一倍,就可以将相邻晶体管触点的镇流区域融合,确保驱动器以及ESD晶体管综合的版图非常紧凑,如图2所示。

第三,设计工程师不用考虑多触点晶体管的ESD性能。最初的设计引入了较大的宏镇流电阻(macro-ballastingresistor),当单触点传导相对较小的ESD电流时,这些宏镇流电阻的作用是快速地增加电压。最近,越来越多的设计都使用动态时序电路为实现所有触点的同时触发提供触发偏置。

(责任编辑:佚名) |